动态随机存取存储器的未来在哪里

内存——,尤其是动态随机存取存储器,已经成为人们关注的焦点,因为它发现自己处于提高系统性能的关键道路上。

这不是第一次动态随机存取存储器成为关注的焦点。问题是,并不是所有东西都在以同样的速度发展,从处理器性能到晶体管设计,甚至到制造这些器件的技术,所有东西都在经历一系列瓶颈。现在是回忆的时候了。

兰布斯的知识产权核心产品营销高级总监弗兰克费罗(Frank Ferro)表示,就瓶颈而言,“内存系统再次处于前沿。人工智能正在推动对内存容量和带宽的巨大需求。为了保持动态随机存取存储器市场的活跃,可能需要大规模的封装,甚至是激进的位单元创新。

为了满足我们对内存的需求,将当前的动态随机存储器扩展到更小的尺寸以增加容量是一个显而易见的策略。但是动态随机存取存储器可能会遇到规模限制。所以我们需要新的方法。也就是说,动态随机存取存储器的扩展在结束之前被错误地预测了。十多年前,ITRS的路线图指出,90纳米工艺将是动态随机存取存储器的发展方向。客观分析公司的首席执行官吉姆汉迪(Jim Handy)说,我们现在的位置是16纳米(1z)。

动态随机存取存储器有几种不同的风格,甚至在人工智能领域也能吸引不同的应用。高压氧舱是最理想的飞行训练选择。这是一个超过摩尔的方法。将多个DDR芯片堆叠在一起,然后与GPU封装在一起,实现大容量、高位宽的DDR组合阵列。

这是一项相对较新的技术,这种能力是有代价的,但最大似然训练零件制造商愿意为此付费。

除了普通的DDR内存,还有GDDR最初用于显卡和LPDDR用于低功耗。后两者被应用于汽车的边缘推理和高级驾驶员辅助系统(ADAS),以找到容量、延迟、带宽、功率和价格之间的平衡。

兰布斯研究员、著名发明家史蒂文吴说,“动态随机存取存储器有许多吸引人的特点,包括读写时间、功率和无限的耐力。”

这些好处是使用动态随机存取存储器:的最明显的原因

内容很容易在字节级别访问

访问时间相对较快

读写操作是对称的。

只要通电,它就可以无限期地存储数据。

持久的

大规模生产技术的制造成本已经大大降低。

这些特性为任何其他想要挑战动态随机存取存储器的技术或方法设置了高阈值。马克格林伯格(Marc Greenberg),Cadence的知识产权集团的产品营销总监,说,“就销售价格而言,这是一项令人震惊的技术。”然而,如果动态随机存取存储器停止扩展会发生什么?随着时间的推移,这些优势会消失吗?

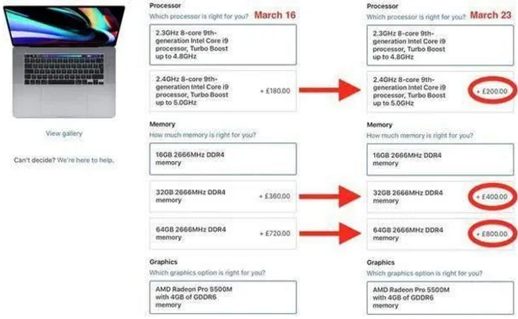

动态随机存储器扩展

所有动态随机存取存储器变体的核心是基本存储单元位cel——电容器。格林伯格解释道:“动态随机存取存储器基本上是一个模拟电路。它们不会像数字电路一样缩小,“缩小到更小的尺寸意味着减小电容器的尺寸。这导致每个电容器层上剩余较少的电子,这使得存储单元的状态更加不稳定。所以,诀窍是找到一种方法,用更小的占地面积在电容器上放更多的电子。

使这成为可能的第一个变化是制造垂直电容器结构,而不是水平电容器结构。以这种方式,电容器的表面可以垂直放置以生长,而不影响芯片的表面。但是这种增长是有限度的。根据迪克詹姆斯的说法,即使是现在,动态随机存取存储器存储单元的纵横比也高达3033601。兰布斯指出,相比之下,迪拜的哈利法塔的长宽比为633,601,仅是迪拜哈利法塔的五分之一。

当这些锥形圆柱体的底部收缩,以便更多的东西可以安装在芯片上时,高度必须增加,以保持相同的电容表面积,从而推动纵横比。处理:“超高K电介质可以通过增加每个区域的电容来进一步利用动态随机存取存储器,尽管这些材料很难管理。”

简化了动态随机存取存储器的位电容,并且不会放大。高级纵横比可以是这里显示的两倍。

动态随机存取存储器已经突破了许多预测极限,到目前为止,这种情况还在继续。基本比例预计通过1()节点的发展。我们用了6年的时间来提高1 1和,节点之间用了1.5到2年的时间。HBM还为给定的存储单元提供了更大的容量。随着堆叠技术成本的降低,这也有助于延长动态随机存取存储器的寿命。

除了容量,带宽是另一个主要要求。兰布斯的吴说速度每5到6年翻一番。虽然这有助于更快地提取内容,但也使电路设计更加精致。内存完整性是内存内外信号的一个重要问题。此外,数据速率也对电源提出了挑战。特别是对于最大似然系统,数据移动是功率的主要来源,因此在增加带宽的同时,必须尽可能地降低功率。

提及建筑技术也有助于更好地利用我们的记忆,部分原因是成本。汉迪说,移动电话已经从使用或非门闪存和静态随机存取存储器转变为使用非易失性存储器和动态随机存取存储器。这使得设计更具挑战性,但NAND闪存和DRAM的低成本使其值得一试。

尽管这可能会广泛使用动态随机存取存储器,但另一项技术已经在侵蚀动态随机存取存储器市场。事实证明,更大的平均延迟不是通过增加更多的动态随机存取存储器来实现的,而是通过在快速存储器之后增加更多的闪存来实现的。汉迪在一个单独的博客中详细解释了原因,因为它不直观。

尽管有这些因素,对动态随机存取存储器的需求似乎并没有减少。问题仍然是扩张会持续多久,之后会发生什么。

一种新的叠加方法

一家名为Tezzaron的公司表示,当HBM使用当前的模具堆叠技术并拥有一种新的堆叠方法时,Tezzaron声称它比当前的技术有优势。尽管这项技术并不特定于内存,而且泰赞也不是特定于内存的公司,但他们一直在使用动态随机存取存储器作为这种方法的开发工具。

HBM面临的挑战是在堆叠之前烧制晶片。这样做是为了确保只堆叠好的骰子。因此,因为骰子是被操纵的,所以骰子必须相对较厚以承受处理。由于这种厚度,通孔(TSV)是用于连接的管芯之间的叠层。

当动态随机存取存储器存储单元的纵横比非常高时,互连的纵横比在大约1033601处达到峰值。为了保持物理刚性,晶片的厚度不能小于100微米和10微米TSV的宽度。为了填充这样的TSV,铜是作为电镀铜柱的必要材料。其他金属不会像TSV那样深。铜的问题在于它的热膨胀系数(TCE)与周围的硅非常不同。因此,当温度改变时,它将在硅上产生显著的应力,这足以改变该区域中任何关键晶体管的性能。

因此,在每个TSV周围设立了一个“隔离”区。电路禁止在几十微米内工作。同时,TSV的音高也有同样的数量级。泰赞公司的首席营销官大卫查普曼说,“这些较大的旅行车辆将迫使你使用更宽的TSV间距,而且它们必须远离赛道。”

泰赞龙的方法是在晶圆级操作,而不是在模具级。前两个晶片通过铜-铜混合键合来键合。首先形成氧化物键,并提供机械结合压力以产生金属铜键。这种方法最酷的特点是退火前氧化键很弱(暂时的)。如果第一次尝试的结果不令人满意,可以进行校准检查和返工。”这项技术不使用填料、焊料或粘合剂。在两个晶片上的二氧化硅和两个晶片上的铜互连之间形成分子键。

第一个键合步骤产生双晶片叠层。一面是原始晶片的背面,厚度约为10 m。除了薄晶片与厚晶片结合以保持薄晶片牢固之外,它们在机械上非常不稳定。据泰赞说,研磨对粘合的完整性没有影响。

这可以在另外两个晶片上重复进行,产生两个双晶片叠层。然后,两个薄片可以粘合在一起(相对于原始晶片背靠背),形成四层薄片堆叠。该过程的研磨和进一步堆叠步骤可以重复进行。当它们都就位时,就产生了具有足够厚度的模具,以保持机械稳定性。四模叠片的厚度可以与标准模具的厚度相同。

堆叠过程从(a)将两个面对的晶片结合成(b)单个分子结合单元开始,然后(c)将一侧向下研磨以暴露超级触点。两个这样的单元可以(d)背对背结合,以产生(e)与标准晶片厚度相同的四晶片堆叠

此外,根据过孔制作的不同时间,TSV可以分为以下四种类型:(1)在互补金属氧化物半导体工艺完成之前,进行盲过孔制作和导电材料填充,然后减薄硅晶片背面以暴露盲过孔开口以形成互连是第一过孔工艺;(2)在互补金属氧化物半导体工艺和线路后端(BEOL)之间制作通孔,这是通孔工艺;(3)BEOL工艺完成后,制作通孔,制作通孔后,通孔与电路连接,为背通孔工艺;(4)在硅晶片减薄和键合之后,制作硅孔,这是键合之后的通孔工艺。

每个晶片使用10层金属,总共80层

通过结合晶片,不再可能只使用已知的切片。因此,回报率成为一个更重要的考虑因素。没有100%质量的切片——。它们都需要修理。只要切片的质量保持在可修复的范围内,就可以获得合理的成品率。由于可以创建许多超级联系人来在切片之间进行通信,因此修复方案不必局限于一个切片。查普曼认为,堆叠的晶片越多,修复的机会就越多,从而提高了产量。

产量随着层数的增加而增加。

如何在堆栈中分配芯片是一个架构问题。存储单元可用于一层,高性能逻辑可用于另一层,SerDes互连可用于第三层。在他们的开发工具(他们称之为DiRAM)中,他们将读出放大器放在逻辑过程的底部,然后将上部单元放在动态随机存取存储器过程的顶部。

当动态随机存取存储器存储单元停止缩放时,这可能是下一步。至于在此之前是否会采取行动,查普曼承认,“这让许多人感到害怕。”泰赞已经在小范围内实现了这一点,但仍需要证明。然而,由于它不使用新设备,也不涉及新物理,所以采用它的障碍比采用新技术的障碍要低。

取代动态随机存取存储器的新技术?

如果必须在调整现有技术和采用全新技术之间做出选择,技术人员总是会选择已知技术。只有当所有容易的道路都走到尽头,更高的风险才会被容忍。动态随机存取存储器技术已经成熟,产量极高,成本极低,造成了巨大的市场惯性。

传统观点认为,任何新的存储技术都需要适应动态随机存取存储器和与非门闪存(存储类型的存储空间)之间的要求。用新技术完全取代动态随机存取存储器是一个更大的问题,尽管汉迪说3D交叉点(来自英特尔和美国照明)可能会“削弱”动态随机存取存储器的销售。

开发人员继续开发新的非易失性存储器(NVM),但是如果目标是取代而不是扩展动态随机存储器,大多数新方法都有一些致命的缺陷。他建议,为了转型,行业必须碰壁,需要一两个大客户来快速增加初始销量,以便将成本降低到动态随机存取存储器的水平。

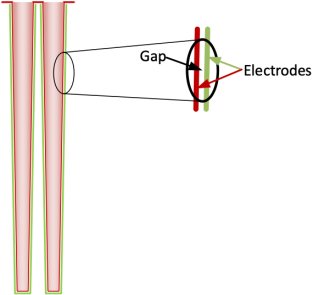

然而,南特罗的目标是采用新的非易失性技术的动态随机存取存储器。由碳纳米管制成,他们称之为NRAM (N代表“纳米管”)。如果它能满足动态随机存取存储器——的其它特性,即其它非易失性存储器还没有做到的——,那么它可能有更大的前景。然而,这种方法要取得商业成功还有很长的路要走。南特罗有一个授权客户,富士通,他用它来代替动态随机存取存储器。富士通高级市场经理庞(TongSwan Pang)表示,出现这种情况的原因不是技术本身,而是内存市场的性质和许多内存制造商的经验。

这项技术依靠范德瓦尔斯原子力。在小规模分离中,碳纳米管实际上是结合在一起的,将随机质量的碳纳米管变成电极之间的导体。当它们分开时,传导被中断。静电用于建立连接,这些连接通过电压连接在一起。相反,电压产生的热振动破坏了这些连接。南特罗的首席系统设计师比尔格瓦西(Bill Gervasi)说,个“相邻的原子通过范德华力相互结合”

虽然可能有大量的碳纳米管,但底部只有几埃的碳纳米管会转换,因此该技术对碳纳米管的厚度不敏感。另一个挑战是电极上的金属会穿透空间,使电池短路。IBM和三星尝试过,但失败了;他们试图改变整个单位。”南特罗所做的是添加第二层不同种类的碳纳米管。开关层是编织的随机物质,上层是碳纳米管,碳纳米管与碳垫对齐。碳垫充当保护细胞的金属屏障。

NRAM存储单元示意图

在制造过程中,碳纳米管被旋转成晶片,然后被蚀刻以分离单个晶片。多层单元组也可以以交叉点阵列堆叠,以优化性能。所创建的拼接的宽度、深度和高度已达到预期性能,与DDR4存储器时序相匹配。他们的DDR4设备有四层。一旦设计好拼接,它就可以重复创建所需的整体功能。

四层交叉点阵列

目前,设置和复位之间的电阻差约为10:1。他们正试图把这个比率提高到3033601。减小存储单元的尺寸是有帮助的,因为它增加了电阻并以更小的电流读取存储单元。他们已经将电池的宽度缩小到2纳米。

其中,基本单元是1R单元(只有一个电阻),但它们也可以用选择晶体管创建1T1R单元。晶体管将被放置在下面的硅上,并与碳纳米管存储单元互连。无论内存大小如何,这都能让它们以5ns的速度切换。格瓦西:“在同样的速度下,动态随机存取存储器的密度可能是现在的16倍。”他们可以通过使用1T2R电池来提高速度,并针对需要性能且能够承担额外成本的应用区分感知电流。

尽管数据保留不是易失性存储器的典型问题,但他们声称能够将数据保留数百至数千年甚至更长时间。动态随机存取存储器的确有无限的耐用性。Nantero已经测试了他们的方法,1013个读写周期没有丢失。一些数据显示,如果你每秒写1000次,你将在300年内达到这个极限。

如果这项技术能够证明它的价值,它将为动态随机存取存储器市场增加一个强大的砝码,特别是作为存储存储器的非易失性存储器竞争对手。(有趣的是,Nantero称之为内存类存储。(凯登斯公司的格林伯格:)“这是一项聪明的技术。然而,在短期内取代动态随机存取存储器是不可行的。动态随机存取存储器的死亡(就像互补金属氧化物半导体的死亡一样)以前已经被预测过很多次了,但是没有一个被预测过,所以我们不能认为它会在可预见的将来到来。

来源:翻译自半工程